分类:模拟锁相环电路/数字锁相环电路

使用数字锁相环集成电路CD4046。由图可见,它有一个方波压控振荡器(VCO)和三个相位比较器。

三个相位比较器分别是:

1.异或相位比较器(NOR),即PC1,其相位锁定范围为0~180o;

2.相位-频率比较器(PFD),即PC2,其相位锁定范围为-360o~360o;

3.JK触发相位比较器(JK),即PC3,其相位锁定范围为0~360o。

锁相环是一种控制晶振使其相对于参考信号保持恒定相位的电路,在数字通信系统中使用比较广泛。目前微处理器或DSP集成的片上锁相环,主要作用则是通过软件实时地配置片上外设时钟,提高系统的灵活性和可靠性。此外,由于采用软件可编程锁相环,所设计的系统处理器外部允许较低的工作频率,而片内经过锁相环微处理器提供较高的系统时钟。这种设计可以有效地降低系统对外部时钟的依赖和电磁干扰,提高系统启动和运行的可靠性,降低系统对硬件的设计要求。

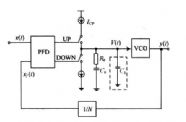

TMS320F28l2处理器的片上晶振和锁相环模块为内核及外设提供时钟信号,并且控制器件的低功耗工作模式。片上晶振模块允许使用2种方式为器件提供时钟,即采用内部振荡器或外部时钟源。如果使用内部振荡器,必须在XI/XCLKIN和X2这两个引脚之间连接一个石英晶体,一般选用30 MHz。如果采用外部时钟,可以将输人的时钟信号直接接到XI/XCLKIN引脚上,而X2悬空,不使用内部振荡器。晶体振荡器及锁相环模块结构如图1 所示。

图1 晶体振荡器及锁相环模块

外部XPLLDIS引脚可以选择系统的时钟源。当XPLLDIS为低电平时,系统直接采用外部时钟或外部晶振作为系统时钟;当XPLLDIS为高电平时,外部时钟经过PLL倍频后为系统提供时钟。系统可以通过锁相环控制寄存器来选择锁相环的工作模式和倍频的系数。表1列出了锁相环配置模式。

表1 锁相环配置模式